解禁時間(テレビ、ラジオ、WEB): 平成20年8月21日(木)13 時30分

(新聞) : 平成20年8月21日(木) 夕刊

平成20年8月21日

報道機関 各位

東北大学電気通信研究所

## スピントロニクス技術を用いた不揮発性集積回路の試作に成功 一磁石と半導体を組み合わせて待機電力をゼロにする新しい集積回路ー

#### 【研究成果】

この度、東北大学電気通信研究所(所長:矢野雅文/以下、東北大)大野英男教授と羽生貴弘 教授は、スピントロニクス技術である磁気トンネル接合(Magnetic Tunnel Junction; MTJ)デバ イスとシリコンデバイスを組み合わせ、不揮発性記憶機能と演算機能を一体化させた不揮発性集 積回路のプロトタイプを試作しました。本集積回路は、プロジェクト参加機関である日立製作所 においてシリコンデバイス部分の作製を行い、スピントロニクスデバイス部分を東北大学電気通 信研究所附属ナノ・スピン実験施設で作製し、世界で初めて集積回路による実証に成功したもの です。

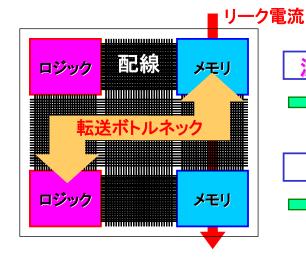

現在の集積回路は、ロジック部とメモリ部が分離されたアーキテクチャであるため、ロジック 部とメモリ部間のデータ転送に大きな遅延が生じるとともに、それに伴う電力消費も極めて増大 するという問題があります。また、通常、メモリ部は揮発性<sup>注1)</sup>のシリコンデバイスを組み合わ せて構成されており、データを保持し続けるために待機時でも常時通電しておかなければならず、 待機電力が著しく増大してしまいます(図1を参照)。これらの問題を同時に解決する1つの方法 <sup>注2)</sup> は、ロジック部とメモリ部を極近くに配置するロジックインメモリアーキテクチャ<sup>注 3)</sup> を採 用し、かつメモリ部を不揮発化することです。不揮発性記憶の性質を有しながら、現有のシリコ ンデバイスを持いたメモリセル回路並みの高速アクセス性・書込み耐性・微細加工の容易性等を 全て有するデバイスは、MTJデバイスです。

今回、東北大の羽生貴弘教授グループにより考案された、MTJデバイスとシリコンデバイスを 組み合わせて高機能性・低消費電力性を有する回路(不揮発性ロジックインメモリ回路)(図3参 照)を、大野英男教授グループの世界最大の磁気抵抗比を実現した材料・デバイス技術を用いて 試作し、その基本動作を実証しました。今回の成果により、両立の難しい高速性と低消費電力性 の双方を兼ね備えた集積回路の実現に道が拓かれました。

本成果は、文部科学省の研究開発委託事業「次世代 IT 基盤構築のための研究開発」の課題の一 つである「高機能・低消費電力スピンデバイス・ストレージ基盤技術の開発」(代表者:大野英男、 東北大学電気通信研究所附属ナノ・スピン実験施設 施設長・教授)において実施されたものです。

### 【不揮発性集積回路とその社会への波及効果】

不揮発性演算素子の開発により、リーク電流が遮断できる VLSI チップの実現が可能となります。

今回試作した回路技術の活用により、現在のシリコンCMOS回路技術において増加の一途をたどる静的消費電力を完全にカットできます。現在、IT機器全体の電力消費のうち、CPUやメモリなど半導体集積チップ部分はおよそ 1/3 程度を占めるといわれております。今回の技術開発により、これらをすべて不揮発性ロジックインメモリ回路で置換することができれば、稼動時以外は電源を遮断できるため、大幅に消費電力を削減できると予想されます。IT機器による電力需要は国全体の 4.7%程度を占めると試算され、稼働率をおよそ 50%とすれば、本プロジェクトの技術開発により我が国全体の電力需要の約 0.4%の削減が期待できます。国全体の電力需要が年間10兆円程度とすれば、本プロジェクトにより年間200億円程度の省エネ効果になります。

また、現在のシリコン CMOS 技術を用いた VLSI チップでは、配線問題に起因する高速化の限界や消費電力の増大も大きな問題となっています。本研究の不揮発性演算素子を用いれば、記憶データを保持しながら待機時の消費電力を完全に遮断できるため、回路を動作させていない時の静的消費電力問題を解決できるだけでなく、記憶・演算機能の一体化構造を小さい面積で実現できるため、配線遅延問題にも大きな効果があります。このように現在の VLSI の問題点を解決できるため、シリコン CMOS に代わる新しい世界標準になることが期待されます。

#### 【従来技術の問題点と本成果による解決】

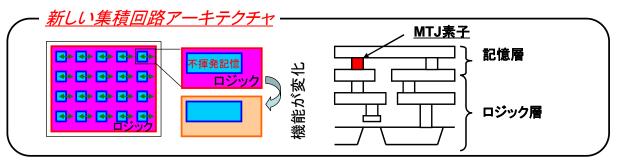

1969年に W. H. Kautz により提案されたロジックインメモリ・アーキテクチャは、ロジック部とメモリ部を分散配置しているため、ロジック部とメモリ部間のデータ転送ボトルネックが解消できることは知られていましたが、このアーキテクチャをシリコンデバイスのみで実現しようとする場合、必ずロジック部とメモリ部を分離して構成しなければならず、また両者の間には信号レベルを変換するためのインタフェースが必要となるため、かえって回路規模が大きくなってしまいアーキテクチャの効果が出せませんでした(図2参照)。これに対し今回、東北大の大野英男教授グループが有する世界最大磁気抵抗比を実現するMTJデバイス技術を用いて、東北大の羽生貴弘教授グループにより考案されていた不揮発性ロジックインメモリ回路のプロトタイプを実際の集積チップ上に試作し、その基本動作を実証することに成功しました。

### 【成果の具体的内容】

#### 1ビットのコンフィギュレーション入力を有する不揮発性演算集積回路の試作に成功

ロジック機能とメモリ機能を融合させた典型的な回路として、FPGA (Field-Programmable Gate Array) に代表されるリコンフィギュラブル回路があります。従来のシリコンデバイスを用いた集積回路では、ロジック部とメモリ部をそれぞれ独立に構成し、最後に2つのブロックを相互に結合するため、回路規模(必要となるシリコンデバイスの個数)が増えてしまいます。これに対し今回の不揮発性集積回路では、シリコンデバイスとその上に製作したMTJ デバイスを直列接続して抵抗分割された電位を出力とします。この結果、(1) ロジック機能とメモリ機能を小さな面積で一体化可能なため、必要となるデバイスの個数を大幅に低減することができる(図5参照)、(2) MTJ デバイスは3次元的に積層されるため、2次元平面上の面積を大幅に削減することができる、の2点が期待されます。なお、今回、不揮発性集積回路のプロトタイプを試作し、基本動作を実測することで提案手法の実現性を実証しました(図6参照)。

## 【成果の意義】

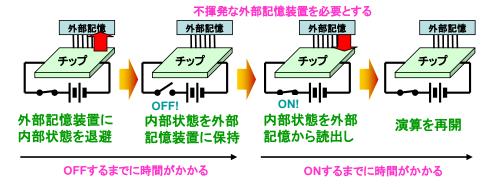

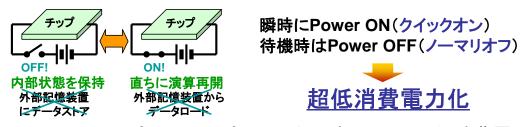

今回開発した不揮発性集積回路では、演算処理に用いられているデータは演算回路内部に分散されているMTJデバイスに記憶されており、電源を切ってもデータを保持することができます。すなわち、低消費電力化する際、従来まで行っていた外付けの不揮発性メモリへのデータ退避/データ再呼出しの操作が一切不要で、瞬時に電源のオン/オフができるシステムの実現(図4参照)へ向けた道を拓いたこととなります。

なお本内容は、日本応用物理学会の論文誌「APEX (Applied Physics Express)」に採択されました (2008年8月22日にオンライン掲載予定)。

- 注1) 入力の電圧信号がカットオフされると、以前の記憶状態が消えてしまう性質。シリコンデバイスの典型例で現在の超微細化集積回路の基本構成要素の MOS (Metal Oxide Semiconductor) トランジスタは、電荷が情報担体であるため、入力の電圧信号がカットオフされると電荷が逃げ (放電され)、以前の記憶状態が消えてしまう。

- 注2) 個別の問題に対しては現在でもそれぞれ対策が施されている。まず、ロジック部とメモリ部が分離されているためにデータ転送遅延が増大する問題を解決する方法として、ロジック部とメモリ部の間に小さい容量のメモリ(キャッシュメモリと呼ぶ)を追加配置し、ロジック部で使いそうなデータを予測して、このキャッシュメモリへ予めデータを移動させておくことで遅延を短縮させる方法が使われている。また、配線材料を工夫する(誘電率kの小さい(low-k)材料にして配線容量への電荷蓄積量を減らす)ことで配線遅延とその電力消費を低減する方法も試みられている。揮発メモリによる待機時の電力消費が増大する問題は、外部に不揮発性メモリ(例えば、フラッシュメモリなど)を追加配置し、ロジック部が待機状態のときメモリ部のデータを外付けの不揮発性メモリへ退避させ、退避完了後に電源をカットオフして待機電力を減らす方法が試みられている。

- 注3) ロジックインメモリアーキテクチャは1969年に W. H. Kautz により提案されたアーキテクチャ。現在主流の CMOS 回路のみによる構成では、①メモリセル回路をコンパクトに構成できない(1 ビットのデータを記憶するフリップフロップ回路に20個のトランジスタ数が必要)、②ダイナミック RAM (Random-Access Memory) セルのようにコンパクトなメモリセル回路の場合、ロジック部との接続にはアンプなどのインタフェース回路が必要となる、など実現することは可能であるが、ロジック部とメモリ部がそれぞれ個別に分離されているため、回路面積が大きくなってしまう問題がありました。

#### ■照会先

東北大学 電気通信研究所 ブレインウェア実験施設 [担当:羽生] 〒980-8577 宮城県仙台市青葉区片平2丁目1-1 電話 022-217-5679 (直通)

# シリコンデバイスのみの集積回路

# 演算器とメモリが分離

➡ 遅延, 面積, 動的消費電力が大

メモリに常時通電

➡ <u>静的電力消費が</u>大

図1. 従来の集積回路アーキテクチャにおける問題点:

図1に示すように、現在のVLSI(超高密度集積回路)は、チップ面積の90%以上を配線領域が占めており、配線による速度の低下と消費電力の増大が、性能向上を阻害している。すなわち、半導体加工の微細化はトランジスタなどの演算素子の速度を向上させたものの、演算素子と膨大な数の記憶素子を結ぶ配線が致命的な性能劣化をもたらしつつある。また、現在主流の記憶素子(SRAMやDRAM)は、データを保持するために待機時に電源供給が必要であり、超微細化のためにオン・オフ比が大きくとれず、リーク電流が流れる。集積素子数が極端に多いVLSIでは、このリーク電流による電力消費が膨大となり、集積度を制限する。IT機器のエネルギー需要は国全体の数10%を占めるようになると言われている現在、低消費電力集積回路の実現自体が社会・経済の発展の基盤形成に不可欠である。

●記憶・ロジックを一体化

(大局的配線を大幅削減)⇒転送遅延を大幅に低減

- ⇒動的消費電力を大幅に低減

- ●記憶が不揮発

(リーク電流を完全に遮断)⇒静的消費電力の完全遮断

(動的再構成に適する) ⇒面積の使用効率の大幅向上

⇒演算機能の可変化など高機能化の可能性

●不揮発性記憶素子はCMOS層の上層に形成

⇒面積削減の可能性

## 図 2. 提案集積回路アーキテクチャ:

図2に示すように、演算器とメモリ間の大局的配線に起因する遅延・消費電力問題は演算回路のすぐそばに記憶回路を配置することで抑制できる。フリップフロップを記憶回路として使った場合、フリップフロップは演算回路内部に配置でき、配線に起因する問題は抑制できるが、回路規模が大きい問題がある。また、SRAM や DRAM を記憶回路として使った場合、記憶回路そのものは小さくできるが、微小な信号差を増幅するためのインタフェースが必要となり、結果として回路規模の増大を招いてしまう。このような問題に対して、羽生貴弘教授グループでは不揮発性メモリ素子の一つである MTJ 素子を活用して演算機能と記憶機能を素子レベルで一体化させる回路技術「TMR ロジック」を提案してきた。TMR ロジックを活用すれば、演算回路と記憶回路がコンパクトに一体化された「ロジックインメモリ回路」が実現でき、演算回路と記憶回路間の配線距離を大幅に短くできるため、遅延・消費電力問題を根本的に解決できる。また、MTJ 素子は MOS トランジスタの直上に積層可能であるため、記憶回路部分の面積を大幅に削減できる。また、不揮発性記憶機能を持っていることから、待機時の電力消費を完全にカットできる。

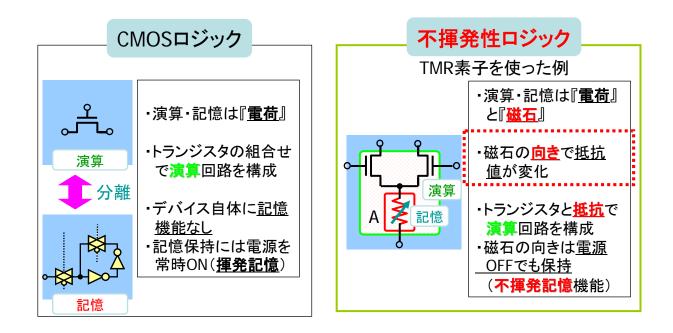

図3. 不揮発性ロジックインメモリ回路によるパラダイムシフト:

図3に示すように、従来のCMOS ロジックに基づく集積回路では、演算回路と記憶回路を別々に構成する必要があった。MOSトランジスタ自体には記憶機能がなく、MOSトランジスタを組み合わせた記憶回路では記憶データを保持するために電源を常時 ONにする必要がある。そのため、回路規模の増大とリーク電流による待機電力の増大を招いてしまう問題がある。これに対して、MOSトランジスタとTMR素子を組み合わせたTMRロジックでは、TMR素子が記憶データに応じて異なる抵抗の大きさを持つことから、MOSトランジスタのON抵抗とOFF抵抗によるスイッチと同様にTMR素子を演算素子としても活用でき、記憶機能だけでなく演算機能を一体化したコンパクトかつ低電力な回路を実現できる。

# ●「揮発メモリ」+「外部記憶装置」による構成(従来)

# ●「不揮発性ロジック」による構成

+内部メモリのパワーマネージメントにより低消費電力化

図 4. ノーマリオフ/クイックオン機能による高速化・低電力化:

図4に示すように、従来の集積回路チップ内のデータを不揮発化するためには、チップ外部に不揮発性記憶装置を用意する必要がある。この構成では、待機時にデータを外部不揮発性装置に退避させ、待機電力をカットすることができるが、データ転送における遅延時間増大および消費電力増大が問題となる。また、演算再開時に外部不揮発性記憶装置からデータを復帰する際も同様の遅延時間増大および消費電力増大が問題となる。これに対し、不揮発性ロジックインメモリ集積回路チップにおいては、不揮発性記憶機能が演算回路と一体化されて内蔵されているため、データの退避および復帰が不要となり、ノーマリオフ/クイックオン動作が可能となる。

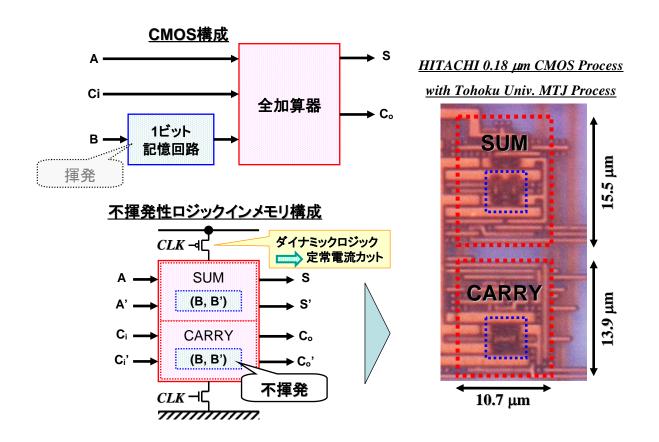

図 5. 不揮発性記憶機能一体型ロジックインメモリ全加算器の試作チップ:

図 5 に示すように、不揮発性記憶機能と演算機能をコンパクトに一体化した全加算器チップを試作しました。CMOS 部分を日立製作所の 0.18um プロセスにて作製し、東北大学にて TMR 素子を作製しました。本試作回路では、ダイナミックロジック形の回路構成を採用し、電源ラインからグランドまで直通する電流パスをカットします。すなわち、クロック信号 CLK= 0 (precharge 相)のとき、出力端容量はともに高電位に設定されます。次に、CLK= 1 (evaluate 相)のとき、差動回路における電流比較(相補出力端からグラウンド間)が行われ、より大電流パスが生じる出力端の電荷が速く抜けることにより、出力電圧が 1 (Low)となります。このように、ダイナミックロジックを活用することにより、電流比較機能を実現しながら貫通電流パスを無くすことができるため、動的消費電力を大幅に低減することが可能となります。また、差動回路方式を採用することにより、小さな TMR 比であっても高速に動作することが可能です。

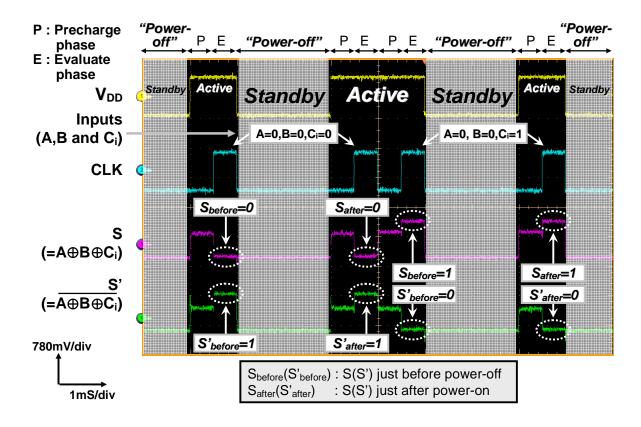

図 6. 試作チップの動作波形:

図 6 に示すように、試作した不揮発性ロジックインメモリ回路に基づく全加算器の基本動作および電源の ON/OFF に伴うクイックオン動作について確認し、世界で初めてシリコンデバイスとスピンデバイスを組み合わせた不揮発性ロジックインメモリ回路の基本動作を実証しました。図 6 の 黄色波形は電源電圧を表しており、L (Low) が待機状態、H (High) が演算状態を示しております。 青色波形はクロック信号を表しており、回路動作のタイミングを示しております。すなわち、CLK=Lのとき、回路は precharge 相で動作し、紫色と緑色波形で示されている両出力信号(S, S')は一定の電位に保持されており、CLK=Hのときに回路は evaluate 相で動作し、差動対回路における左右のネットワークで電流比較を行い、その結果として相補出力(S, S')が決定されます。本試作回路は不揮発記憶機能が演算回路内部に一体化され、内蔵されているため、電源の ON/OFF を行っても、回路の内部データが変化することはありません。そのため、図 6 に示すように、 $S_{before}$  (S'  $_{before}$ )と  $S_{after}$  (S'  $_{after}$ )は同じ結果となり、電源 OFF 前のデータ退避および電源 ON 後のデータ復帰が不要で、クイックオン動作が可能です。