Press Release

2023年9月28日

報道機関 各位

国立大学法人東北大学 株式会社 CUSIC

# 結晶構造が異なる SiC 同士のシームレスな積層に成功

**─ パワー半導体の電力損失を大幅に削減できる見通しを得る ─**

### 【発表のポイント】

- 同時横方向エピタキシャル成長法 (注 1) により、結晶構造が立方晶の 3C-SiC (注 2) 結晶を六方晶の 4H-SiC 基板上に結晶格子をシームレスに (切れ目なく) 積層させることに成功しました。

- SiCパワー半導体デバイスにおける電力損失低減と長期信頼性が両立できる新規デバイス構造(CHESS-MOS®)(注 3) 実現の見通しが得られました。

- SiC パワーMOSFET デバイスの電力損失の原因となる界面準位 (注 4) の 密度が 200 分の 1 以下に低減されることを実証しました。

- 3C-SiC/4H-SiC/3C-SiC/4H-SiC のような二重量子井戸構造 (注 5) の形成が 確認され、高周波デバイス・高周波集積回路の実現の可能性が示され ました。

- 高温下や放射線にさらされる宇宙空間・原発廃炉作業場でも誤動作・ 故障が生じにくい長期信頼性に優れた集積回路の実現が期待されます。

#### 【概要】

世界中で実用化が進められている SiC パワー半導体デバイスにおいて、SiC の物性に由来する根本的問題を克服する新技術の開発が望まれています。株式会社 CUSIC (仙台市、代表取締役・長澤弘幸) が考案し権利化した新しいパワー半導体デバイス (CHESS-MOS®) はその有力候補で、異なる結晶構造・物性値を持つ 3C-SiC と 4H-SiC を積層させたハイブリッド構造基板によって実現されることが特徴です。

この度、東北大学電気通信研究所の櫻庭政夫准教授と佐藤茂雄教授、東北大学未来科学技術共同研究センターの長康雄特任教授、そして株式会社 CUSIC の研究グループは、共同研究を進める中で、3C-SiC と 4H-SiC を積層させた

ハイブリッド構造基板を同時横方向エピタキシャル成長法(SLE 法; Simultaneous Lateral Epitaxy Method)を用いて製作することに世界で初めて成功しました。さらに、絶縁膜を形成したハイブリッド構造基板表面の界面準位密度を走査型非線形誘電率顕微鏡法(SNDM 法; Scanning Nonlinear Dielectric Microscopy Method) によって計測した所、3C-SiC 表面の密度を4H-SiC 表面の 200 分の 1 以下まで大幅に低減できることを実証しました。これらのことから、SiC パワーMOSFET デバイスの長期信頼性が大幅に向上するのみならず、電力損失を 30%以上削減でき、SiC パワー半導体デバイスを用いたシステムの高性能化・新機能創出と省エネルギー化の両立に大きく貢献できることが期待されます。

本研究成果は 2023 年 9 月 18~22 日にイタリアで開催された国際会議 International Conference on Silicon Carbide and Related Materials (ICSCRM2023) と第84回応用物理秋季学術講演会 (2023年9月19~22日、熊本)で発表されました。また、今後、国際会議 MRS Fall Meeting & Exhibit (2023年11月26日~12月1日、アメリカ)でも発表される予定です。

## 【詳細な説明】

## 研究の背景

近年、電車や電気自動車のモータ駆動制御に不可欠となる高温環境でも安定動作する高耐圧半導体デバイスとして、SiC(炭化珪素;シリコンカーバイド)の単結晶基板を用いたパワー半導体デバイスの実用化が世界中で進められております。しかしながら、電力損失低減や長期信頼性の観点では、基板として用いる SiC 単結晶の持つ物性そのものに由来する根本的な問題点が指摘されており、それらを克服する新しい技術の開発が望まれていました。

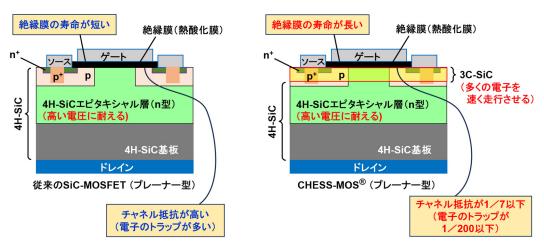

株式会社 CUSIC (仙台市、代表取締役・長澤弘幸) は、SiC パワー半導体デバイスの電力損失低減と長期信頼性確保を同時に実現する技術として、新しいパワー半導体デバイス (CHESS-MOS®) (図 1) を考案しました。CHESS-MOS®は、同じ SiC 単結晶でありながら異なる結晶構造・物性値を持つ3C-SiC と 4H-SiC を積層させたハイブリッド構造基板によって実現されるものであり、3C-SiC 層には"長期にわたって安定的に多くの電子を速く走行させる役割"、そして、4H-SiC 層には"高い電圧に耐える役割"を割り当てることで、電力損失低減と長期信頼性の両立を可能とします。このような CHESS-MOS®の実現には、3C-SiC と 4H-SiC を結晶格子をシームレスに積層させるための新しい基板加工技術と結晶成長技術が必要不可欠でした。

#### 今回の取り組み

この度、東北大学電気通信研究所の櫻庭政夫准教授と佐藤茂雄教授、東北

大学未来科学技術共同研究センターの長康雄特任教授、そして株式会社 CUSIC の研究グループは、CHESS-MOS®の実現に向けた共同研究を進める中で、3C-SiC と 4H-SiC を積層させたハイブリッド構造基板を同時横方向エピタキシャル成長法(SLE 法; Simultaneous Lateral Epitaxy Method)を用いて製作することに世界で初めて成功しました。さらに、絶縁膜(熱酸化膜)を形成したハイブリッド構造基板表面の界面準位密度を走査型非線形誘電率顕微鏡法(SNDM法; Scanning Nonlinear Dielectric Microscopy Method)によって計測した所、3C-SiC 表面の密度は 4H-SiC 表面の 200 分の 1 以下となり、SLE 法によって界面準位密度を大幅に低減できることを実証しました。過去のパワー半導体デバイス製作から得られている知見を参照すると、上記のような低い界面準位密度が達成されれば、CHESS-MOS®を取り入れることにより、電力損失が30%以上削減できる見通しとなります。

## 今後の展開

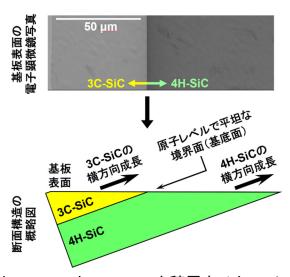

SLE 法は、4H-SiC 基板から延伸する 4H-SiC 基底面の上面に 3C-SiC が結晶成長し、その 3C-SiC もまた 4H-SiC 基底面に沿って延伸するという原理を利用しているので、3C-SiC 層と 4H-SiC 基板の界面が 1 原子分の高さの狂いもなく平坦に形成されることが特徴ということになります。このため、3C-SiC 層内の自由電子は界面近傍を散乱されることなく高速に走行できるようになり、さらなる電力損失低減と高速動作につながることが期待されます。

また 3C-SiC が 4H-SiC よりも大きな電子親和力を有することから、CHESS-MOS®の絶縁膜/SiC 界面に形成される電子に対する障壁は、4H-SiC よりも圧倒的に高くなると考えられます。この効果により、絶縁膜を通して漏洩する電流密度は激減し、絶縁膜が短期間で劣化してしまうこともなくなります。すなわち、SiCパワー半導体デバイスの長期信頼性が大幅に向上し、SiCパワー半導体デバイスを用いたアプリケーションの市場が大きく拡大することが期待されます。

さらに SLE 法の実験において、3C-SiC/4H-SiC/3C-SiC/4H-SiC のような二重量子井戸構造が形成される現象も確認されました。このような SiC 積層構造を意図的に形成することにより、これまで、SiC 半導体デバイスでは困難であると考えられてきた高周波デバイス実現への道も開ける可能性が出てきます。さらに、SLE 法で半絶縁 4H-SiC 基板上に 3C-SiC 結晶を成長させることで、半導体基板との静電結合による高周波信号減衰の問題を回避できるため、既存の SiC パワー半導体デバイス生産ライン用いた高周波集積回路の量産への道も開かれると考えられます。

集積回路の基板材料としても広く用いられている Si に比べ、SiC を基板に用いると熱や放射線に起因する誤動作や故障が起こりにくいことが知られて

います。本成果により SiC の集積回路への応用の道が開かれるならば、高温下 や放射線にさらされる宇宙空間・原発廃炉作業場などの過酷環境でも誤動作・ 故障が生じにくい集積回路の実現につながることが期待されます。

SLE 法は、これまで構築されてきた SiC パワーMOSFET デバイスの形状や製造プロセスを大きく変更することなく、SiC 基板表面の一部に異なる結晶構造を導入できる点が特徴であり、多くの SiC パワー半導体デバイス生産ラインに取り入れられていくことが期待されます。

図 1. SiC パワーMOSFET デバイスの断面図。(左) 従来の 4H-SiC 基板を用いた場合、(右) 4H-SiC 基板に CHESS-MOS®を取り入れた場合。

図 2. SLE 法により 3C-SiC と 4H-SiC を積層させたハイブリッド構造基板の (上) 基板表面の電子顕微鏡写真、(下) 断面構造の概略図。(基底面に対して 基板表面は傾いている。わかりやすくするために、概略図では実際より傾きを 強調してある。)

### 【謝辞】

名古屋工業大学の宮川鈴衣奈助教には SLE 前の SiC 加工処理、有限会社ドライケミカルズ(宮城県名取市)代表取締役の千葉哲也氏にはシングルドメイン 3C-SiC を得るためのステップアラインメント処理を実施していただきました。

#### 【用語説明】

- 注1. エピタキシャル成長法:結晶基板の表面において、表面原子配列周期 (原子間隔)を引き継ぎながら結晶が成長していくこと。成長方向の原子 配列が同じとは限らない。SiC のエピタキシャル成長中に 4H-SiC 基板か ら延伸する 4H-SiC 基底面の上面に 3C-SiC が結晶成長し、その 3C-SiC も また 4H-SiC 基底面に沿って延伸するような結晶成長方法を同時横方向 エピタキシャル成長法 (SLE 法; Simultaneous Lateral Epitaxy Method) と 呼ぶ。基底面を境界として、3C-SiC と 4H-SiC が上下にくっきり分かれた 積層構造が形成される。

- 注2. SiC (炭化珪素;シリコンカーバイド):シリコン(Si)と炭素(C)の組成比 1 対 1 の共有結合性の化合物半導体結晶材料。Si (シリコン)単結晶と比較して、絶縁破壊電界強度は 10 倍、バンドギャップは 2~3 倍ほども大きいことから、高い電圧が掛かるパワー半導体デバイスに用いられる。化学組成は同じでも約 200 種類もの異なる原子配列の結晶構造(結晶多形、ポリタイプ)が見つかっている。代表的なものとして立方晶の 3C-SiC、六方晶の 4H-SiC と 6H-SiC が知られている。

- 注3. CHESS-MOS® (Cubic and Hexagonal Epitaxially Stacked SiC MOSFET): エピタキシャル成長によって 3C-SiC と 4H-SiC を積層させた 基板を用いて製作される金属ー絶縁体ー半導体電界効果トランジスタ (MOSFET; Metal-Oxide-Semiconductor Field-Effect Transistor)。特許第 6795805 号。

- 注4. 界面準位:絶縁膜と半導体の界面近傍に生じる準位であり、電子を捕獲したり、放出したりするもの。MOSFET の性能を低下させる原因と考えられている。

- 注5. 量子井戸構造:キャリア(電子やホール)が超薄膜中に閉じ込められ、 キャリアの自由度が制限されているような構造。エネルギーバンド構造の 異なる材料を接合させた界面近傍に生じることがある。通常の3次元の

自由度を持つバルク材料とは異なった新しい物性を発現する。

注6. 走査型非線形誘電率顕微鏡法(SNDM 法; Scanning Nonlinear Dielectric Microscopy Method): 走査型顕微鏡の探針を対象物質表面に近接させた状態で、物質内部の局所的な電荷の偏り(分極)を計測する方法。探針を2次元的に走査しながら計測することで、場所ごとの電荷の偏りやすさを二次元的に可視化(マッピング)することができる。

## 【会議情報】

- [1] "SNDM study of MOS interface state densities on 3C-SiC and 4H-SiC stacked structure" (Oral Presentation), Hiroyuki Nagasawa, Yasuo Cho, Maho Abe, Takenori Tanno, Michimasa Musya, Masao Sakuraba, Yusuke Sato and Shigeo Sato, International Conference on Silicon Carbide and Related Materials (ICSCRM2023, September 19-22, 2023, Sorrento, Italy), Session: Process 2: MOS II, September 19, 2023, 11:40-12:00.

- [2] 「3C-SiC/4H-SiC 積層構造 MOS 界面の SNDM 評価」(ロ頭発表)、 長 康雄 1、長澤 弘幸 2、櫻庭 政夫 3、佐藤 茂雄 3 (1. 東北大学未来 科学技術共同研究センター、2. 株式会社 CUSIC、3. 東北大学電気通信 研究所)、第 84 回応用物理秋季学術講演会 (2023 年 9 月 19~23 日、 熊本), 2023 年 9 月 21 日(木) 14:45~15:00、講演番号: 21p-B201-6.

- [3] "SNDM Study on Cubic and Hexagonal Epitaxially Stacked SiC MOS Interfaces" (Poster Presentation), Yasuo Cho, Hiroyuki Nagasawa, Masao Sakuraba and Shigeo Sato, 2023 MRS Fall Meeting & Exhibit (November 26-December 1, 2023, Boston, USA), Symposium: CH01: Advanced Characterization Methods of Energy Material Applications, November 28, 2023, 20:00-22:00.

## 【問い合わせ先】

(研究に関すること)

東北大学電気通信研究所

准教授 櫻庭政夫

TEL: 022-217-5549

Email: sakuraba.masao\*myad.jp(\*を@に置き換えて下さい)

(報道に関すること)

東北大学電気通信研究所総務係

TEL: 022-217-5420

Email: riec-somu\*grp.tohoku.ac.jp (\*を@に置き換えて下さい)