平成28年5月13日

報道機関 各位

東北大学 国際集積エレクトロニクス研究開発センター

# 高集積・高歩留まり2メガビット磁気ランダムアクセスメモリ (STT-MRAM) の実証実験に世界で初めて成功

単位メモリセル面積30%の低減と70%の歩留まり向上(対従来比)を同時に実現

# 【概要】

国立大学法人東北大学(総長:里見進/以下、東北大学)国際集積エレクトロニクス研究開発センターの遠藤哲郎センター長(兼 同大学大学院工学研究科教授)のグループは、磁気トンネル接合素子(Magnetic Tunnel Junction, MTJ)と相補型金属酸化膜半導体(Complementary Metal Oxide Semiconductor, CMOS)電界効果トランジスタとを接続するコンタクトホールの直上に、性能劣化なく磁気接合素子を成膜する技術の開発に世界で初めて成功いたしました。今回の成功は、新たに設計・試作した2メガビット(2百万ビット)スピン・トランスファー・トルク型磁気ランダムアクセスメモリ(STT-MRAM)に、上記の新開発技術を適用して行った実験にて、従来比70%以上の歩留まり率向上を実証することで確認されました。本技術は、STT-MRAM の単位メモリセル面積を30%縮小させ、商品化を大きく促進させる成果です。

今回の開発の成功は、東北大学国際集積エレクトロニクス研究開発センターで推進している CIES コンソーシアム事業での材料技術、プロセス技術、および回路設計・評価技術にいたる、集積エレクトロニクス分野における上流から下流までの一貫した開発体制によるものです。

## 問い合わせ先

東北大学国際集積エレクトロニクス研究開発 センター 支援室長 門脇豊

電話 022-796-3410

E-mail:support-office@cies.tohoku.ac.jp

東北大学国際集積エレクトロニクス研究開発 センター戦略企画部門 部門長 大嶋洋一

電話 022-796-3406

E-mail:support-office@cies.tohoku.ac.jp

# 【背景】

最近のシリコン CMOS メモリ集積回路においては、トランジスタ微細化に伴って消費電力が増大し、高密度化が阻害されるという問題が深刻になっています。この問題を解決する一つの有力な手法として、メモリ集積回路に、電源を切断しても記憶を維持できる「不揮発性」という機能を導入するという手法があります。この手法を用いると、記憶の保持に電力を必要としなくなるため、メモリ集積回路を含むシステムの大幅な低消費電力化が可能となります。この手法の実現に向けて世界中の大学、研究所、企業などの各機関において、新しい不揮発材料を搭載したメモリ集積回路の研究開発が活発に行われています。

そのような新規不揮発メモリ集積回路の中で、東北大学国際集積エレクトロニクス研究開発センター 遠藤哲郎センター長のグループでは、世界最高水準のスピントロニクス素子である磁気トンネル接合素子(MTJ)の開発と共に、それを用いた「磁気ランダムアクセスメモリ(STT-MRAM)」の開発に取り組んでいます。MTJは、他の種類の不揮発性素子(※1)に比べ、高速データ書き換え、低電圧動作、高繰り返し動作耐性という特長を持ちます。このため、同素子を用いた STT-MRAM は、従来の DRAM や SRAM 等の、いわゆる「ワーキングメモリ(※2)」の領域への応用に向け最も有望なメモリ集積回路です。

### 【研究課題】

DRAM などの既存メモリに匹敵する高密度な STT-MRAM の実現に向けての鍵は、記憶の単位となる基本回路(メモリセル)内のトランジスタと MTJ とを可能なかぎり小面積に収めることです。一方で、MTJ は磁性を用いた素子であるために、MTJ 下部の電極の品質も重要です。例えば、下部電極表面の凹凸が大きいなど、形状が荒れている場合、磁歪や、ビラリ効果(※3)などの影響により素子特性が劣化するという問題があります。このため、従来の STT-MRAM においては、CMOS 回路と MTJ 素子とを接続する箇所においては、両者を互いに接続する集積回路の機構である「コンタクトホール」の直上を避け、わざとずらした位置に MTJ を配置していました。これは、一般にコンタクトホール上の電極では、コンタクトホールの穴の形状を反映して凹面状になるなど、表面形状が平坦でなく、その上に MTJ を成膜すると上記の特性劣化の問題が生ずるためです。しかしながらこの手法は同時に、メモリセル面積の増大を招いており、DRAM など従来のメモリ集積回路に対し、小面積という観点で及ばないという大きな課題がありました。

# 【研究経緯】

東北大学国際集積エレクトロニクス研究開発センター 遠藤哲郎センター長のグループは、上記のメモリセル小面積化および MTJ 性能劣化という相反する問題を解決するための技術開発をかねてより進めてまいりました。

まず最初に、MTJ を積載する下部電極表面に専用の研磨技術を開発し、この研磨技術を 適用した MTJ に対しては、コンタクトホール直上に MTJ を成膜しても特性を劣化させない ということを、単体 MTJ 素子レベルを用いた基礎実験で確認いたしました。この成果はす でに 2014 年 9 月の固体素子材料国際会議(International Conference on Solid State Devices and Materials, SSDM)にて発表しております(S. Miura 他、発表番号 A-6-3)。

#### 【研究手法と成果】

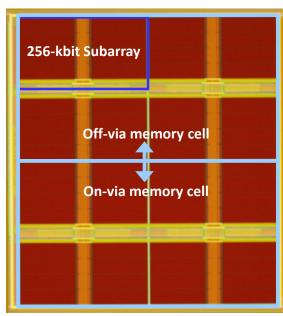

上記の基礎実験の成果を受けて、この技術をメガビット(百万個)クラスの多数 MTJ を有する実際のメモリ集積回路に適用してその有効性を実証するため、2 メガビット(200 万ビット)の性能実証用 STT-MRAM テストチップの設計、試作を行いました。この性能実証用2 メガビット STT-MRAM チップの特徴は次のとおりです。

・東北大学にて開発した専用読み出しアンプ回路の搭載、および外部入力により最適設

定が可能な参照電圧(※4)を導入することで、高感度なデータ読み出し回路を実現しました。これにより、STT-MRAM の読み出し性能に寄与する MTJ の主要特性である MR 比 (※5) が試作時の目標値 100%のところ 40%程度でも正しくデータ判別できるようになり、高精度な読み出しが可能となりました。

・コンタクトホール直上の位置と、ずらした位置との双方に MTJ を配置したメモリセルを、同一メモリ回路上に半々で混在させることで、条件を統一して両メモリセル形状の比較を可能にしました。

この新設計の2メガビットSTT-MRAMテストチップを用い、我々の開発したコンタクトホール直上MTJ成膜技術を適用したものと適用しないものの双方を試作し、両者を評価したところ、同技術を適用したSTT-MRAMは、同技術なしでコンタクトホール直上にMTJを積載したSTT-MRAMに比べると歩留りが70%向上することが実験により確認されました。また、メモリセル面積が30%増大するコンタクトホール直上からMTJをずらして配置した従来形式のSTT-MRAMと比べて同等の歩留りが得られることもわかりました。

## 【研究成果の意義】

以上の実証実験により、本技術の有効性がメガビットクラスのメモリセルを有する実際の STT-MRAM においても実証されました。この結果は、STT-MRAM のチップ面積を従来の DRAM などと同等までに小面積化し、実用化を促進する結果です。

以上、このたびの一連の技術開発により、単体素子レベルでの成果を集積回路レベルにまで進展させたこの成果は、東北大学国際集積エレクトロニクス研究開発センターで推進している CIES コンソーシアム事業での材料技術、プロセス技術、および回路設計・評価技術にいたる、集積エレクトロニクス分野における上流から下流までの一貫した開発体制により得られたものです。今後とも当センターでは上記の開発体制の特長を生かし、集積エレクトロニクス分野において世界をリードする成果を目指して研究開発活動を進めてまいります。

以上の成果は、2016年5月16日~18日の間、フランス、パリで開催されるメモリ集積回路に関する国際学会である「米国電気電子学会(※6)国際メモリワークショップ(IEEE International Memory Workshop)」で発表いたします。

なお、本研究は、国際集積エレクトロニクス研究開発センターにて推進している CIES コンソーシアム事業の支援を受けて得られた成果です。

#### 【用語説明】

(※1) 他の種類の不揮発性素子

強誘電体素子、相変化素子、電界誘起抵抗変化素子などがある。それぞれの素子から、 強誘電体メモリ (FeRAM)、相変化メモリ (PCRAM)、抵抗変化メモリ (ReRAM) が作られる。 (※2) ワーキングメモリ

コンピュータシステムを構成するメモリのうち、比較的高速(数 10MHz~数 GHz)で動作するメモリ。従来の CMOS メモリでは、ダイナミックランダムアクセスメモリ(DRAM)やスタティックランダムアクセスメモリ(SRAM)がその代表格。

(※3) 磁歪、ビラリ効果

磁界の変化により磁性体が変形したり、逆に磁性体への圧力印加による変形で磁気特性が変化する現象。

(※4) 参照電圧

MRAM の読み出し動作にあたり、読み出したデータが"0"か"1"かの判定に必須な電圧。

(※5) MR 比

MTJ の"0"状態と"1"状態の抵抗比パーセンテージを表す性能パラメータ。値が大きいほど優れた性能。

# (※6) 米国電気電子学会

The Institute of Electrical and Electronics Engineers, Inc. 通称 IEEE (アイ・トリプル・イー)。米国に本拠を置く世界最大の電気・電子技術に関する学会組織。

コンタクト直上 MTJ 成膜技術の集積回路レベルでの実証のために設計・試作された 2-Mbit STT-MRAM チップ写真