**Press Release**

平成30年12月5日

報道機関 各位

東北大学 国際集積エレクトロニクス研究開発センター

# 100Mb 超密度で世界最高書き込み速度性能(14 ナノ秒)を 有するキャッシュアプリケーション向け 128Mb 密度 STT-MRAM の開発に成功

#### 【概要】

指定国立大学法人東北大学国際集積エレクトロニクス研究開発センター(以下、CIESと略称)の遠藤哲郎センター長(兼 同大学大学院工学研究科教授、先端スピントロニクス研究開発センター(世界トップレベル研究拠点)副拠点長、省エネルギー・スピントロニクス集積化システムセンター長、スピントロニクス学術連携研究教育センター 部門長)のグループは、CIESコンソーシアム産学共同研究プロジェクト「不揮発性ワーキングメモリを目指したSTT-MRAMとその製造技術の研究開発」プログラム、科学技術振興機構 戦略的創造研究推進事業(研究代表者:遠藤哲郎)において、100Mb超密度で世界最高書き込み速度性能(14ナノ秒)を有するキャッシュアプリケーション向け128Mb密度STT-MRAM(磁気ランダムアクセスメモリ)の開発に世界で初めて成功致しました。今回の実証実験の成功は、本学国際集積エレクトロニクス研究開発センターが推進するCIESコンソーシアム並びに、科学技術振興機構戦略的創造研究推進事業によるものです。

以上の成果は、2018年12月1日~5日の間、米国サンフランシスコで開催される電子デバイスに関する国際学会である「米国電気電子学会(※2)国際電子デバイス会議(IEEE International Devices Meeting)」で発表致します。

## 【背景】

最近のシリコンベースの集積回路では、トランジスタの微細化に伴う揮発性半導体メモリにおける待機電力(※3)の増大が、高性能化を阻害する大きな問題となっております。この問題を解決して集積回路の持続的な発展を牽引する技術として、スピントロニクス技術を使った不揮発性メモリの混載が高い注目を集めております。スピントロニクスとは、これまで別々に用いられてきた電子が有する電気的な性質(電荷)と磁気的な性質(スピン)の両方を用いることで新しい物理現象の発見や新しい機能を有するデバイスの実現を目指す学術分野です。スピントロニクス技術を用いた代表的なデバイスは、

磁気トンネル接合です。磁気トンネル接合(MTJ)は、磁石の性質を有する材料で構成された二つの層で薄い絶縁層を挟んだ構造を有し、二つの層の磁石の向きが平行な場合と反平行な場合で異なる抵抗を示します。二つの抵抗状態をそれぞれディジタル情報の0と1に割り当てることでランダムアクセスメモリとして応用することができます。STT-MRAMでは、情報を磁石の方向として保存しますので不揮発性(電源を切っても情報を忘れない性質)を有します。不揮発性に加えて、高速動作、低電圧動作、高い書き換え耐性というこれまで揮発性半導体メモリが使われてきた領域に必要とされる特性を全て満足することから、世界中で積極的に研究開発が行われており、大手半導体会社が2018年の実用化を目指すことをアナウンスしております。

#### 【研究課題】

STT-MRAM は、その最初の応用先として混載メモリが最も有望視されています。表 1 には、STT-MRAM と従来技術の混載メモリである eFlash メモリと SRAM(※4)の性能を比較しました。従来技術である eFlash と比べると、STT-MRAM では、セル面積(メモリ密度)はほぼ同程度であるものの、電源電圧を低減できるために低消費電力化でき、更に書き換え耐性が高いために信頼性を向上できます。一方、SRAM と比較するとセル面積が減少できるために高密度化でき、更に不揮発性により低消費電力化できます。これらのキャッシュアプリケーションなどの混載メモリへの応用を目指す場合には、STT-MRAMの高密度化していく必要があります。これまでの混載メモリ応用を目指したSTT-MRAMの報告では、大手ファウンドリ会社からの報告でも8Mb-40Mbであり、更なる高密度化が望まれていました。

表1 従来技術の混載メモリの性能と STT-MRAM の性能の比較。

表中のFは、feature sizeで、最小加工寸法。図中の数字は、2017年に開催された IEEE International Electron Devices Meetings のショートコースの資料から抜粋した一例。

|                      | SRAM                          | SRAM 置き換え用<br>STT-MRAM       | 混載<br>フラッシュ              | 混載 Flash 置き換え用<br>STT-MRAM  |

|----------------------|-------------------------------|------------------------------|--------------------------|-----------------------------|

| メモリセル<br>サイズ         | 160-200 <i>F</i> <sup>2</sup> | 70-100 <i>F</i> <sup>2</sup> | 40 <i>F</i> <sup>2</sup> | 50-60 <i>F</i> <sup>2</sup> |

| 電源電圧 (V)             | 0.6 - 1.2                     | 1.2                          | ≥ 10                     | 1.2                         |

| 書き込み電流<br>(A)        | 10 <sup>-5</sup>              | 10 <sup>-5</sup>             | 10 <sup>-5</sup>         | 10 <sup>-5</sup>            |

| 読み出し/書き<br>込み時間 (ns) | ≤ 2/≤ 2                       | 5/10                         | 10/20000                 | 25/200                      |

| 情報保持時間               | 揮発性                           | 1 か月                         | > 20 年以上                 | 15年                         |

| 書き換え耐性<br>(cycles)   | 10 <sup>16</sup>              | 10 <sup>14</sup>             | 10 <sup>5</sup>          | 108                         |

## 【研究経緯】

東北大学国際集積エレクトロニクス研究開発センター 遠藤哲郎センター長 (兼 同大学大学院工学研究科教授、先端スピントロニクス研究開発センター(世界トップレベル研究拠点))のグループでは、CIES コンソーシアムでの産学共同研究、科学技術振興機構 戦略的創造研究推進事業(ACCEL)「縦型BC-MOSFET による三次元集積工学と応用展開」にて、STT-MRAM の性能向上と高密度化の研究開発に取り組んでまいりました。

#### 【研究手法と成果】

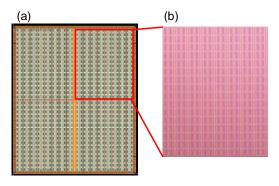

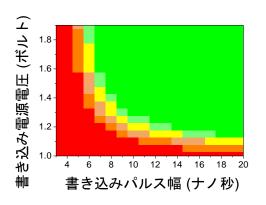

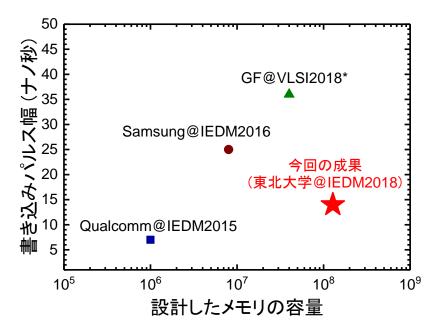

高密度 STT-MRAM を実現するためには、半導体テクノロジーノードの微細化に加えて、STT-MRAM 中で記憶素子として用いられる MTJ 素子の微細化も必要です。本研究では、MTJ 素子を 39nm まで微細化すると共に、更にメモリセルの構造を工夫し、MTJ を集積回路の後工程で作製される Via と呼ばれる電極上に作製することで、メモリセルの面積を減少させることに成功しました。また、同メモリセルを用いて、128Mb 密度の STT-MRAM を設計し、実際に試作しました。図 1(a) 設計した 128Mb 密度の STT-MRAM の設計図面と、(b) に試作した同 STT-MRAM の一部のチップ写真を示しました。更には試作した同 STT-MRAMのサブアレイにおいて高速動作特性を評価し、1.2V という低い電源電圧で 14ナノ秒という高速動作の実証に成功しました(図 2)。図 3 には、他のグループからの STT-MRAM の発表と本発表での結果を比較したものを示します。本研究で得られた成果は、これまでの報告に比べて、設計したメモリ容量が大きく、且つ高速で動作できていることが分かります。

本研究では、高密度(大容量)STT-MRAM の製造で必要となる MTJ の微細化、メモリセルの微細化を行い、微細化したメモリセルを用いて、混載メモリ用としては世界最高密度である 128Mb 密度の STT-MRAM を設計・試作しました。この結果、100Mb 超密度の STT-MRAM としては、世界最高書き込み速度性能(14ナノ秒)となる 128Mb 密度 STT-MRAM の開発に世界で初めて成功致しました。

## 【研究成果の意義】

今回、CIES は、CIES コンソーシアムで推進している CIES 産学共同研究プロジェクト「不揮発ワーキングメモリを目指した STT-MRAM とその製造技術の研究開発」プログラム、科学技術振興機構 ACCEL にて、混載メモリ用途としては世界で初めてとなる 128Mb 密度の STT-MRAM を設計・試作し、同 MRAM を用いて 100Mb 超密度の STT-MRAM としては、世界最高速となる 14 ナノ秒という高速動作を実証しました。今回開発された技術により、大容量(高密度)混載 STT-MRAM 製造への道が切り拓かれ、IoT や AI チップ等に広く用いられるキャッシュアプリケーションなど、STT-MRAM の応用範囲が更に拡がることが期

待されます。

以上の成果は、2018年12月1日~5日の間、米国サンフランシスコで開催される電子デバイスに関する国際学会である「米国電気電子学会(※2)国際電子デバイスミーティング(IEEE International Electron Devices Meeting)」で発表致します。

#### 【用語説明】

#### (※1) 書き換え耐性

メモリに保存された情報を何度書き換えられるかを示す指標。磁気トンネル接合では、動作速度の向上や不揮発性の向上により、書き換えるために必要となる電圧が高くなるために、情報を書き換えるために繰り返し電圧を印加すると、極薄で形成されている絶縁膜が壊れる。故障しないで書き換えられる回数が書き換え耐性の評価指数として用いられる。

## (※2) 米国電気電子学会

The Institute of Electrical and Electronics Engineers, Inc. 通称 IEEE (アイ・トリプル・イー)。米国に本拠を置く世界最大の電気・電子技術に関する学会組織。

# (※3) 待機電力

集積回路が動作していないときにも消費してしまう電力の事。トランジスタの微細化に伴うリーク電流の増大により主に揮発性メモリ部分で増加している。

#### (※4) eFlash メモリと SRAM

eFlash メモリ:フラッシュメモリの一種でランダムアクセス性があるために集積回路中の混載メモリとして用いられる。

SRAM (スタティックランダムアクセスメモリ): 混載メモリの一種で揮発性 半導体メモリ。高速動作に利点がある一方で、メモリセルのサイズが大きい ために主に小容量のキャッシュメモリとして用いられる。汎用コンピュータ ーでは、SRAM に加えて大容量で低速で動作する DRAM (ダイナミックランダム アクセスメモリ)も一緒に用いられる。

図 1(a) 本研究で設計した 128Mb 密度の STT-MRAM の設計図面。(b) 実際 に試作した 128Mb 密度の STT-MRAM のサブアレイのチップ写真。

図2 本研究で試作した128Mb 密度の STT-MRAM 内のサブアレイの高速動作 特性の評価結果。

図3 本研究で設計・試作した128Mb 密度のSTT-MRAMの書き込み特性と他のグループの過去の報告との比較。(\*GF@VLSI2018については、電源電圧が1.4Vで、MTJのスイッチングにクロックの半分を消費したと仮定して計算。)

# 【問い合わせ先】

- ◆研究内容及びセンターの活動に関して 東北大学国際集積エレクトロニクス研究開発センター センター長・教授 遠藤哲郎 TEL: 022-796-3410

- ◆その他の事項について

東北大学国際集積エレクトロニクス研究開発センター

支援室長 門脇豊 TEL: 022-796-3410 FAX: 022-796-3432

E-mail: support-office@cies.tohoku.ac.jp

東北大学国際集積エレクトロニクス研究開発センター内

OPERA 支援室長 山川佳之 TEL: 022-796-3405

E-mail:opera-shien@grp.tohoku.ac.jp