2016年 | プレスリリース・研究成果

高集積・高歩留まり2メガビット磁気ランダムアクセスメモリ(STT-MRAM)の実証実験に世界で初めて成功

単位メモリセル面積30%の低減と70%の歩留まり向上(対従来比)を同時に実現

国立大学法人東北大学国際集積エレクトロニクス研究開発センターの遠藤哲郎センター長(兼 同大学大学院工学研究科教授)のグループは、磁気トンネル接合素子(Magnetic Tunnel Junction, MTJ)と相補型金属酸化膜半導体(Complementary Metal Oxide Semiconductor, CMOS)電界効果トランジスタとを接続するコンタクトホールの直上に、性能劣化なく磁気接合素子を成膜する技術の開発に世界で初めて成功いたしました。

今回の成功は、新たに設計・試作した2メガビット(2百万ビット)スピン・トランスファー・トルク型磁気ランダムアクセスメモリ(STT-MRAM)に、上記の新開発技術を適用して行った実験にて、従来比70%以上の歩留まり率向上を実証することで確認されました。本技術は、STT-MRAMの単位メモリセル面積を30%縮小させ、商品化を大きく促進させる成果です。

今回の開発の成功は、東北大学国際集積エレクトロニクス研究開発センターで推進しているCIESコンソーシアム事業での材料技術、プロセス技術、および回路設計・評価技術にいたる、集積エレクトロニクス分野における上流から下流までの一貫した開発体制によるものです。

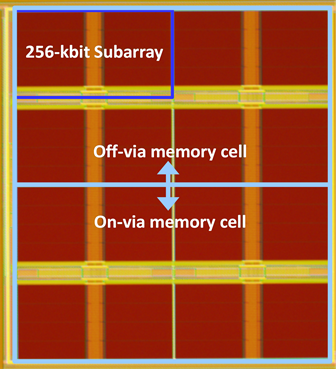

コンタクト直上MTJ成膜技術の集積回路レベルでの実証のために設計・試作された 2-Mbit STT-MRAM チップ写真

問い合わせ先

東北大学国際集積エレクトロニクス研究開発センター

支援室長 門脇豊

電話:022-796-3410

E-mail:support-office*cies.tohoku.ac.jp(*を@に置き換えてください)

東北大学国際集積エレクトロニクス研究開発センター戦略企画部門

部門長 大嶋洋一

電話:022-796-3406

E-mail:support-office*cies.tohoku.ac.jp(*を@に置き換えてください)