2018年 | プレスリリース・研究成果

メモリ・テスト・システムによる、 磁気ランダム・アクセス・メモリ(STT-MRAM)の スイッチング電流測定技術を確立 -アドバンテストとの共同研究、STT-MRAMの不良解析と実用化に大きく前進-

【概要】

指定国立大学法人東北大学国際集積エレクトロニクス研究開発センターの遠藤哲郎センター長(兼 同大学大学院工学研究科教授、先端スピントロニクス研究開発センター(世界トップレベル研究拠点)副拠点長、省エネルギー・スピントロニクス集積化システムセンター長、スピントロニクス学術連携研究教育センター 部門長)のグループは、CIESコンソーシアムでの産学共同研究並びに、科学技術振興機構 産学共創プラットフォーム共同研究推進プログラム(領域統括:遠藤哲郎)において、株式会社アドバンテスト(代表取締役 兼 執行役員社長:吉田 芳明 本社:東京都千代田区丸の内1丁目6番2号 以下、アドバンテスト)と共同で、次世代メモリとして期待される「スピン注入型磁気ランダム・アクセス・メモリ(STT-MRAM)」のメモリ・アレイ内のスイッチング電流を高精度かつ高速に測定する電流測定モジュールを開発し、アドバンテスト社製のメモリ・テスト・システムを用いてマイクロアンペア単位かつナノ秒単位で測定する実証実験に成功しました。

今回の実証実験の成功は、本学国際集積エレクトロニクス研究開発センター(略称CIES)が推進するCIESコンソーシアム並びに、東北大学が幹事機関を務め、東北大学・京都大学・山形大学と先進的企業群の力を結集して、産学共創プラットフォームの形成を目指すOPERAにおける開発体制によるものです。

以上の成果は、2018年10月22日~24日に仙台で開催された国際学会「米国電気電子学会(※1) 不揮発性メモリ技術シンポジウム(IEEE Non-Volatile Memory Technology Symposium)」で発表しました。

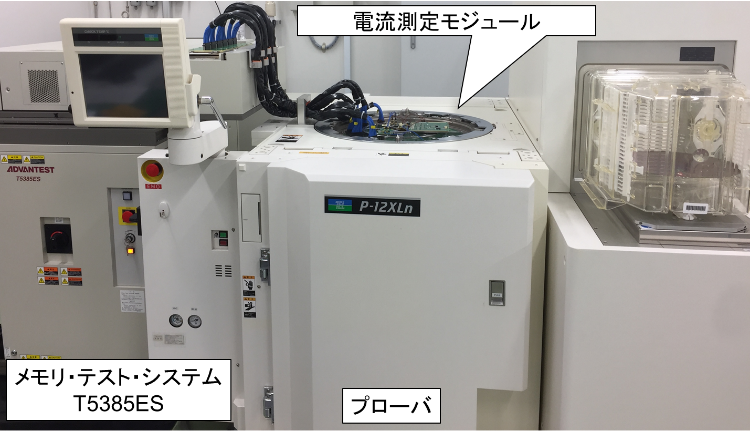

図1:STT-MRAMの評価に用いたメモリ・テスト・システム(T5385ES)と試験環境

【用語説明】

※1)米国電気電子学会 The Institute of Electrical and Electronics Engineers, Inc. 通称 IEEE (アイ・トリプル・イー)。米国に本拠を置く世界最大の電気・電子技術に関する学会組織。

問い合わせ先

研究内容及びセンターに活動に関して

東北大学国際集積エレクトロニクス研究開発センター

センター長・教授 遠藤哲郎 TEL:022-796-3410

その他の事項について

東北大学国際集積エレクトロニクス研究開発センター内

OPERA支援室長 山川佳之 TEL:022-796-3405

E-mail:opera-shien*grp.tohoku.ac.jp (*を@に置き換えてください)