2024年 | プレスリリース・研究成果

省エネ半導体の切り札STT-MRAMの極限微細化技術を確立 ~1桁ナノメートル領域にてAIから⾞載まで利用可能に~

【本学研究者情報】

〇東北大学電気通信研究所 教授 深見俊輔

研究室ウェブサイト

【発表のポイント】

- 省エネ・高性能半導体実現の切り札としてスピン移行トルク磁気抵抗メモリ(STT-MRAM)(注1)の社会実装が進行。

- 将来の一桁ナノメートル領域にて、AI/IoTから車載まで幅広いアプリケーションでの要求性能に応じてSTT-MRAMの記憶素子をカスタマイズする材料・構造技術を確立し、動作実証。

- STT-MRAMの高性能化による社会実装の拡大を支える基盤として期待。

【概要】

不揮発性メモリ(電源を切っても情報が保持されるメモリ)は半導体の大幅な省エネ化をもたらすと期待されており、人工知能(AI)、もののインターネット(IoT)から車載まで幅広いアプリケーションでの利用に向けて研究開発が進められています。特にスピントロニクス(注2)技術を利用したスピン移行トルク磁気抵抗メモリ(STT-MRAM)は、大手半導体デバイスメーカーから1X ナノメートル世代[注3]の車載向け半導体への導入が発表されるなど注目を集めています。より微細化が進んだ将来の半導体回路で幅広いアプリケーションに対応するためには、STT-MRAMの記憶素子である磁気トンネル接合(MTJ)素子そのものの微細化とともに、アプリケーション毎で異なる高速性や高温でのデータ保持特性などの要求性能を満たしていく必要があります。

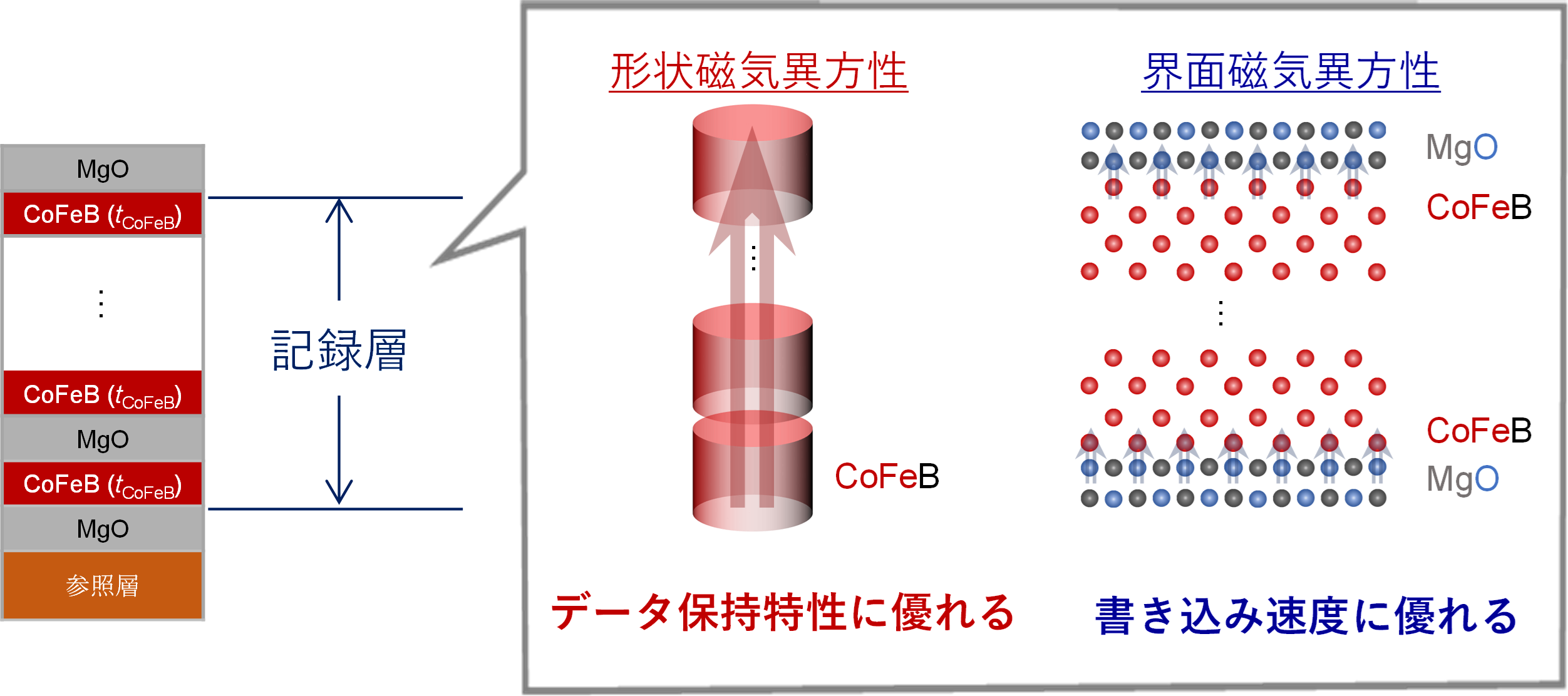

今回、東北大学電気通信研究所の五十嵐純太学術研究員(当時)、同大学材料科学高等研究所(WPI-AIMR)の陣内佛霖助教(当時)、深見俊輔教授、大野英男教授(現総長)らは、直径一桁ナノメートル領域で様々なアプリケーションの要求性能に応じてカスタマイズできる磁気トンネル接合(MTJ)素子(注4)を提案し、その材料・構造の設計指針を体系化しました。MTJにCoFeB/MgO材料系からなる積層磁性層構造を導入し、その膜厚や積層回数を変化させて、車載応用に必要な高温での高いデータ保持特性やAI/IoT用途で求められる高速でのデータ書き込み特性を直径一桁ナノメートルの極微細領域でそれぞれ満たすことができることを実証しました。

これは、STT-MRAMが将来の極微細世代の半導体技術にて幅広い用途に展開可能であることを示す重要な成果です。また本研究で提案した構造は、大手半導体デバイスメーカーの既存設備により形成可能であり、今後のSTT-MRAMのスケーリングを支え、社会実装範囲を拡大する基盤となることが期待されます。

本研究成果は、2024年1月4日(英国時間)に論文誌npj Spintronicsに掲載されました。

図1. 本研究で提案した積層磁性層構造。データ保持特性を重視する場合、CoFeB層膜厚を厚くし、CoFeB/MgO層の積層回数を少なくすることで形状磁気異方性の割合を増やす。書き込み速度を重視する場合、CoFeB層膜厚を薄くし、CoFeB/MgO層の積層回数を増やすことで界面磁気異方性の割合を増やす

【用語解説】

注1. スピン移行トルク磁気抵抗メモリ(STT-MRAM)

磁気抵抗変化型ランダムアクセスメモリの次の世代の磁性体メモリで、電流注入によってデータを書き込むタイプのMRAM(エムラム/Magnetoresistive Random Access Memory)

注2. スピントロニクス

電子の持つ電気的性質(電荷)と磁気的性質(スピン)を同時に利用することで発現する物理現象を明らかにし、工学的に利用することを目指す学術分野。例えば従来は不可能であった磁気的性質や磁化方向の電気的な検出や制御(スピン移行トルク(STT)磁化反転)、電気伝導特性の磁場や磁化による制御などが可能となり、現在も様々な現象が発見され続けている。

注3. 半導体テクノロジーノード (1Xナノメートル世代、Xナノメートル世代、オングストローム世代など)

半導体集積回路はその構成要素となる電界効果トランジスタのサイズや配線のピッチを縮小することで性能が向上する。トランジスタのサイズや配線のピッチの特徴的な長さスケールでテクノロジーノード、すなわち半導体製造技術の世代(例:45ナノメートル世代、32ナノメートル世代、22ナノメートル世代、...)が定義され、18ヶ月毎に集積度が2倍になるというムーアの法則に従って微細化が進められてきた。ただし現在ではトランジスタや配線ピッチの物理的な長さと技術世代は必ずしも対応はしていない。 1Xナノメートル世代は10ナノメートル台、Xナノメートル世代は10ナノメートル未満のテクノロジーノードの総称である。現在3ナノメートル世代の半導体製造技術による製品が販売され、2ナノメートル世代の研究開発が進んでいる。オングストローム(0.1ナノメートル(100億分の1メートル)を表す長さの単位)世代の半導体製造技術は、2ナノメートル世代以降の半導体製造技術である。MTJは半導体集積回路の配線層間に形成され、一般的にそのサイズはテクノロジーノードの数倍となる。一桁ナノメートルサイズのMTJ素子は2ナノメートル世代以降の半導体集積回路において必要となる。

注4. 磁気トンネル接合(MTJ)素子

磁性体 / 絶縁体 / 磁性体の三層構造からなる構造。2つの磁性体の磁化が平行な場合に抵抗が低く、磁化が反平行な場合に抵抗が高くなる(これはトンネル磁気抵抗効果と呼ぶ)。一方の磁性体の磁化が固定され、他方の磁性体の磁化がそれに対して平行、反平行の2状態を取るように設計することでデジタル情報を記憶するメモリ素子として機能する。メモリ素子では、抵抗値を測定することでビット情報を読み出すことができ、また磁化の向きを反転することで情報を書き込むことができる。

問い合わせ先

(研究に関すること)

東北大学電気通信研究所

教授 深見 俊輔

TEL: 022-217-5555

E-mail: s-fukami*tohoku.ac.jp(*を@に置き換えてください) (兼)東北大学先端スピントロニクス研究開発センター (CSIS)

(兼)東北大学国際集積エレクトロニクス研究開発センター (CIES)

(兼)東北大学材料科学高等研究所 (WPI-AIMR)

(兼)稲盛科学研究機構 (InaRIS)

(報道に関すること)

東北大学電気通信研究所 総務係

TEL: 022-217-5420

E-mail: riec-somu*grp.tohoku.ac.jp(*を@に置き換えてください)

![]()

![]()

![]()

東北大学は持続可能な開発目標(SDGs)を支援しています