2025年 | プレスリリース・研究成果

次世代型磁気メモリSOT-MRAMの書き込み電力35%減に成功 ─AIのための消費電力低減に寄与するメモリ技術に道筋─

【本学研究者情報】

〇国際集積エレクトロニクス研究開発センター

センター長 遠藤哲郎

東北大学研究者紹介

【発表のポイント】

- スピン軌道トルク磁気記憶メモリ(SOT-MRAM)(注1)素子技術を進化させ、高速動作性能は維持しつつも書込み動作電力をこれまでより35%削減し、世界最小の低消費電力の動作実証に成功しました。

- 高速動作に有利なスピン軌道トルク素子の低消費電力動作技術の開発は、SOT-MRAMの課題の解決に道筋を付けるものであり、未だ研究開発フェーズに留まっているSOT-MRAMの実用化に大きく貢献すると期待されます。

【概要】

全世界で人工知能(AI)の利用が拡大するにつれ、コンピューターがますます膨大なエネルギーを消費する問題が起こっています。コンピューターのエネルギー消費を抑えるため、特に素子の低消費電力化が重要な課題になっています。

東北大学国際集積エレクトロニクス研究開発センター長(以下、CIES)はこれまでSOT-MRAM技術の研究開発分野でリードし、世界に先駆けCMOS(注2)技術に融合したメモリ素子を開発して10年データ保持特性を持ちながら0.35ナノ秒の超高速データ書込み動作およびSOT-MRAMチップの動作実証に成功してきました。

今回、CIESの遠藤哲郎センター長(※)のグループは、300mmウェハ技術(注3)に融合したSOT-MRAMメモリ素子技術をさらに進化させ、従来の10年データ保持特性(熱安定性E /kBT=70)と0.35ナノ(10億分の1)秒の超高速データ書込み性能を維持しながら、新たにその書込み動作電力をこれまでより35%削減した世界最少の低消費電力の動作実証に成功しました。

今回のメモリ素子開発は、文部科学省「次世代X-nics半導体創生拠点形成事業」における「スピントロニクス融合半導体創出拠点」プログラム(拠点長:遠藤哲郎)並びに本学CIESが推進するCIESコンソーシアムの成果です。

以上の成果は、2025年5月18日~21日の間、米国カリフォルニア・モントレで開催される半導体メモリデバイス技術に関する主要な国際学会である米国電子情報学会主催の「国際メモリワークショップ(IEEE International Memory Workshop)」で発表します。

(※:以下の職を兼務。東北大学大学院工学研究科教授、電気通信研究所教授、先端スピントロニクス研究センター(世界トップレベル研究拠点)副センター長、スピントロニクス学術連携研究教育センター領域長)

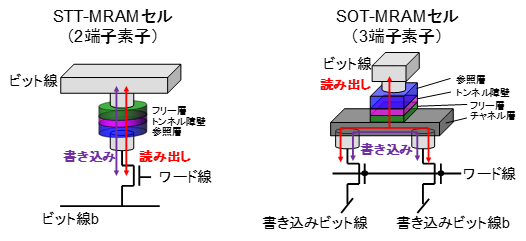

図1. STT-MRAMセルとSOT-MRAMセルのイメージ図

【用語解説】

注1. スピン軌道トルク磁気記憶メモリ(SOT-MRAM)

記憶素子として磁性体素子MTJを用い、MTJの磁石の向きで"0" "1"情報を記憶する不揮発性メモリMRAMの一種。代表的なMRAMにはスピン移行トルク型(STT)とスピン軌道トルク型(SOT)があります。STT-MRAMは電子機器に組み込むマイコンの不揮発性フラッシュメモリやSRAMのラストレベルキャッシュの置き換えとして応用展開されていますが、数ナノ秒以下で動作するSRAMキャッシュのような高速メモリへの適用は難しい。SOT-MRAMはこの問題を解決できるため、数ナノ秒以下の高速メモリ用として研究開発が進められています。

注2. CMOS

Complementary Metal Oxide Semiconductorの略で、「相補型金属酸化膜半導体」を意味します。CMOSは、p型とn型のMOSFETを組み合わせる特徴を持つ半導体要素回路です。

注3. CMOS集積回路技術

CMOSチップの製造は複数の工程から成っています。一般的に、p型とn型のMOSFETをシリコンウェハ基板上に形成する為の複数の工程(前工程)と、複数の配線層を上層へ形成する為の配線層工程(後工程)があり、これらは安定した製造を確保するために最適化された設計ルールや製造工程条件を適用します。

【論文情報】

タイトル:Low write power and Field-free sub-ns write speed SOT-MRAM cell with Design Technology of Canted SOT structure and Magnetic Anisotropy for NVM

著者: Thi Van Anh Nguyen, Hiroshi Naganuma, Hiroaki Honjo, Yoshihiro Sato, Takaho Tanigawa, Shoji Ikeda and Tetsuo Endoh*

*責任著者:東北大学 国際集積エレクトロニクス研究開発センター センター長 教授 遠藤 哲郎

掲載誌:Conference, IEEE国際メモリワークショップ(IEEE International Memory Workshop)

URL: https://ewh.ieee.org/soc/eds/imw/

※著者の所属先一覧については、下記の詳細PDFをご覧ください。

問い合わせ先

(研究内容およびセンターの活動について)

東北大学国際集積エレクトロニクス研究開発センター

センター長・教授 遠藤 哲郎

TEL: 022-796-3410

(*を@に置き換えてください)

(その他の事項について)

東北大学国際集積エレクトロニクス研究開発センター

支援室長 三上 洋一

TEL: 022-796-3410

FAX: 022-796-3432

Email: support-office*cies.tohoku.ac.jp

(*を@に置き換えてください)

![]()

![]()

![]()

東北大学は持続可能な開発目標(SDGs)を支援しています