2020年 | プレスリリース・研究成果

SOT-MRAMチップの動作実証に初めて成功 ~読み書き同時処理機能の実装により、実用化に向け大きく前進~

【発表のポイント】

- スピントロニクス技術とCMOS技術の融合により、スピン軌道トルク型磁気トンネル接合(SOT-MTJ)素子を用いた不揮発メモリ(SOT-MRAM)チップの試作・実証に初めて成功

- スピントロニクス技術を用いた不揮発メモリチップとしては初となるデュアルポート動作(読み書き同時処理)の実装に成功

- 無磁場環境下における高速動作(60MHz書込み、90MHz読出し)を達成

- 開発回路技術により、高速スタティックランダムアクセスメモリ(SRAM)の置き換えが期待されるSOT-MRAMの更なる高速動作化への道を拓く

【概要】

半導体メモリでは、トランジスタの微細化に伴い、待機電力の増大が課題になっており、この問題を解決するために、スピントロニクス技術を使った不揮発性メモリに注目が集まっています。東北大学国際集積エレクトロニクス研究開発センター(以下、CIES)の遠藤哲郎センター長・教授※と電気通信研究所の羽生貴弘教授、夏井雅典准教授らの研究グループは、スピン軌道トルク型磁気トンネル接合(SOT-MTJ)素子とSi-CMOS技術を組み合わせた集積回路技術を用いて、高速なデータの読み書きを可能とするデュアルポート型SOT-MRAMチップを試作し、その動作実証に初めて成功しました。この不揮発性メモリ技術は、ICT社会基盤のパラダイムシフトをもたらし、Society5.0を実現するための基盤技術として期待されます。

本実験は、内閣府 革新的研究開発推進プログラム(ImPACT)ならびに本学CIESが推進するCIES コンソーシアムによるものです。

本成果は、2020年6月15日~18日にオンライン開催される、集積回路技術に関する世界最高峰の国際会議の一つである「VLSIシンポジウム2020(VLSI2020:2020 Symposia on VLSI Technology and Circuits)」で発表されました。

※:以下の職を兼務:東北大学大学院工学研究科教授、電気通信研究所教授、先端スピントロニクス研究センター(世界トップレベル研究拠点)副センター長、スピントロニクス学術連携研究教育センター領域長

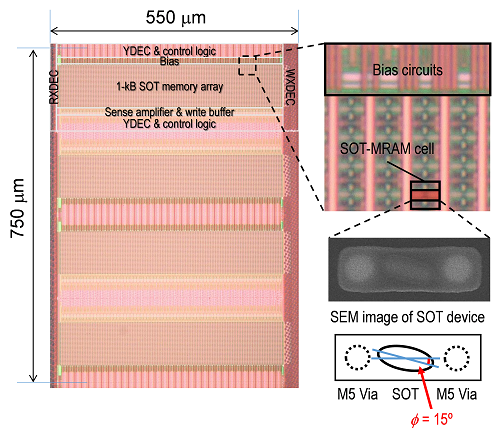

図1 開発した4キロバイトのデュアルポート型SOT-MRAMチップの写真。

問い合わせ先

◆研究内容(回路設計および動作検証)について

東北大学電気通信研究所

教授 羽生 貴弘 TEL:022-217-5679

准教授 夏井 雅典 TEL:022-217-5552

◆プロジェクト内容・研究内容(集積技術)について

東北大学国際集積エレクトロニクス研究開発センター

センター長・教授 遠藤 哲郎 TEL:022-796-3410

◆その他の事項について

東北大学国際集積エレクトロニクス研究開発センター 支援室

室長 髙橋 嘉典 TEL:022-796-3410 FAX:022-796-3432

E-mail:support-office*cies.tohoku.ac.jp(*を@に置き換えてください)