2024年 | プレスリリース・研究成果

正しい並列処理をこなす確率的アルゴリズムを開発 〜省エネ・高速な次世代コンピュータへの一歩〜

【本学研究者情報】

〇電気通信研究所 准教授 鬼沢直哉

ウェブサイト

【発表のポイント】

- 次世代コンピュータの「確率ビット(注1)」がたくさん同時に動くと、計算ミスが大きくなる原因を見つけました。

- 確率論的コンピュータ(注1)の速度と正確さを同時に改善する新しい方法を開発しました。

- 次世代の低消費電力デバイスとして知られる確率ビットによる確率論的コンピュータの発展と、機械学習・人工知能への応用が期待されます。

【概要】

確率ビット(pビット)によるコンピュータは、現在のトランジスタを用いた決定論的計算(注2)を行うコンピュータと比較して大幅な省エネルギー化が期待されている一方で、計算アルゴリズムを並列処理させると、正答率が大幅に低下する問題がありました。これまで、この問題の原因が特定出来なかったため、pビットによる確率論的コンピュータの応用先は限定的でした。

東北大学電気通信研究所の鬼沢直哉准教授と羽生貴弘教授らの研究グループは、シミュレーションによりpビット同士の相互干渉が問題であることを特定しました。さらに、pビットを部分的に働かせなくすることで、相互干渉を効率的に防ぐアルゴリズムを開発しました。その結果、確率論的コンピュータの正答率を大幅に向上させるだけでなく、並列処理による高速化も達成しました。

今後、次世代の省エネルギーデバイスとして期待されるpビットに基づく確率論的コンピュータにおいて、機械学習やデータサイエンスの分野で新たな展開をもたらし得るものと期待されます。本研究成果は2024年1月16日付で科学誌Scientific Reportsでオンライン公開されました。

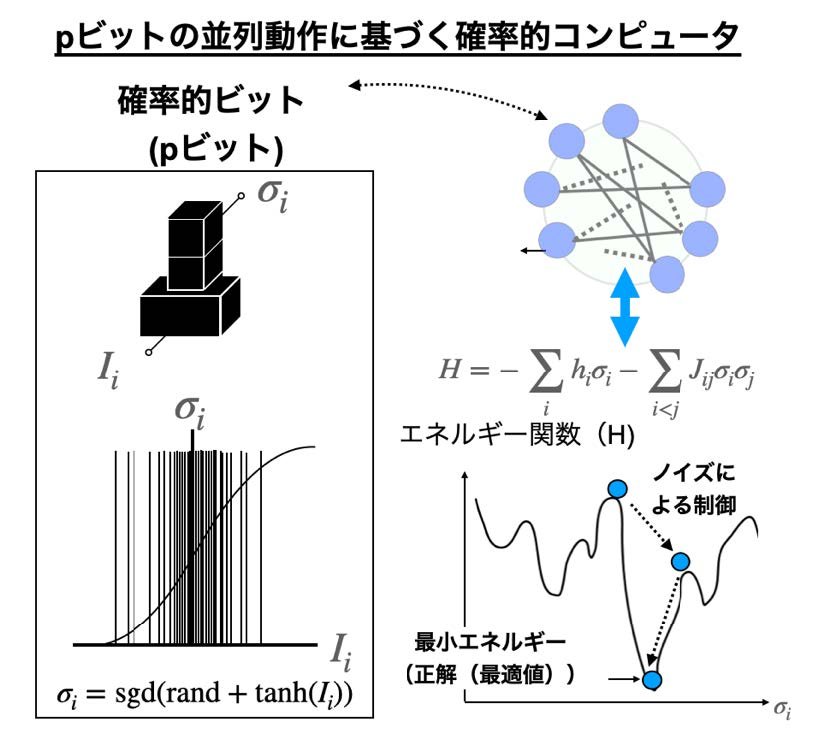

図1. 確率ビット(pビット)を並列動作させる確率論的コンピュータとの概要図。この確率論的コンピュータでは、まず問題をエネルギー関数にマッピングをし、pビットによる確率的動作をさせることでエネルギーを最小化することで、正解が得られる。

【用語解説】

注1. 確率ビット(pビット)、確率論的コンピュータ

確率ビットは出力信号が0と1の間で確率的に変化するもので、確率的コンピュータの基本情報単位。

注2. 決定論的計算と確率的計算

現在のコンピュータは、入力情報から出力情報が一意に決まる決定論的計算に基づく。一方で、確率論的計算では出力を一意に決定せず、主に統計的な手法に基づく出力を決定する計算技術。

問い合わせ先

(研究に関すること)

東北大学電気通信研究所

准教授 鬼沢直哉

TEL:022-217-5546

Email: naoya.onizawa.a7*tohoku.ac.jp(*を@に置き換えてください)

(報道に関すること)

東北大学電気通信研究所

総務係

TEL: 022-217-5420

Email: riec-somu*grp.tohoku.ac.jp(*を@に置き換えてください)

![]()

![]()

![]()

東北大学は持続可能な開発目標(SDGs)を支援しています